-

Rev. 1.0

Feb 2006

#### Disclaimer

The information in this manual has been carefully checked and is believed to be accurate. Eurotech assumes no responsibility for any infringements of patents or other rights of third parties, which may result from its use.

Eurotech assumes no responsibility for any inaccuracies that may be contained in this document. Eurotech makes no commitment to update or keep current the information contained in this manual.

Eurotech reserves the right to make improvements to this document and/or product at any time and without notice.

#### Warranty

This product is supplied with a limited warranty. The product warranty covers failure of any Eurotech manufactured product caused by manufacturing defects. Eurotech will make all reasonable effort to repair the product or replace it with an equivalent alternative. Eurotech reserves the right to replace the returned product with an alternative variant or an equivalent fit, form and functional product. Delivery charges will apply to all returned products.

#### Trademarks

All trademarks, both marked and not marked, appearing in this document are the property of their respective owners.

© 2007 Eurotech Spa

Eurotech S.p.A. A member of the Eurotech Group Via Fratelli Solari, 3/a 33020 - AMARO (UD) ITALY

## Conventions

The following table lists conventions used throughout this guide.

#### Warnings and Important Notices:

**Warning:** Information to alert you to potential damage to a program, system or device or potential personal injury

Information note: Indicates important features or instructions to observe (This page is intentionally left blank.)

# **Table of Contents**

| Conventions                                                                                                                                                                                                                                                                                                         |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Table of Contents                                                                                                                                                                                                                                                                                                   | 5                                                                                      |

| Chapter 1 The Soft Power Management                                                                                                                                                                                                                                                                                 | 7                                                                                      |

| Chapter 2 CPU-1450 SPM block diagram architecture<br>Intel 82801 ICH2 and System Power States<br>System Power Planes<br>Power Management interface signals<br>Event Input Signals and Their Usage                                                                                                                   |                                                                                        |

| Chapter 3 CPU-1450 Power management connections<br>Ethernet<br><i>The Eurotech Ethernet Transceiver</i><br>Serial 1 & Serial 2<br>Auxiliary Power Connector<br>Electrical connections                                                                                                                               |                                                                                        |

| Development Kit connections                                                                                                                                                                                                                                                                                         |                                                                                        |

| Chapter 4 SPM Management<br>Entering Low Power mode                                                                                                                                                                                                                                                                 | 22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>25 |

| Intel® 82801BA I/O Controller Hub 2 (ICH2)<br>PM1_STS Power Management 1 Status Register<br>PM1_EN—Power Management 1 Enable Register<br>PM1_CNT—Power Management 1 Control Register<br>GPE0_EN—General Purpose Event 0 Enables Register<br>SuperIO National PC87364<br>Super I/O Configuration D Register (SIOCFD) |                                                                                        |

| Chapter 6 Software examples<br>Wake on RTC alarm<br>Wake on Ring Indicator Pulse<br>Wake on LAN (Ethernet)                                                                                                                                                                                                          |                                                                                        |

| Chapter 7 CPU power consumption                                                                                                                                                                                                                                                                                     |                                                                                        |

| Chapter 8 Appendix<br>Related Software<br>Related Documents                                                                                                                                                                                                                                                         |                                                                                        |

(This page is intentionally left blank.)

## Chapter 1 The Soft Power Management

Soft Power Management (SPM) is a technique that allows users to put the CPU module into a low power mode (therefore decreasing power consumption) while keeping the capacity to restart work as soon as something happens.

When the CPU-1450 module is powered off with SPM, just a little part of the board remains supplied. This part monitors the system inputs, looking for wake-up events.

The low power mode can be activated via software or via a power button, whereas can be deactivated by either the power button or from one of a number of wake-up events (i.e. receiving packets from network line, or an alarm at a predetermined time).

(This page is intentionally left blank.)

## Chapter 2 CPU-1450 SPM block diagram architecture

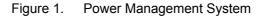

The CPU-1450 is a PC/104-Plus module realized with a mezzanine architecture approach and comprises of two modules:

- Celeron Processor Module

- PIII Carrier

For better understanding of the Power Management functionality of the CPU-1450 we have shown the following block logic architecture that focuses on the chipset that manages the power saving functions. In the diagram the dotted lines show the previous block differences.

Consider that the Celeron Processor Module is fully ACPI compatible but the PIII Carrier has been developed with the support for APM-based legacy power management for non-ACPI implementations. In conclusion the complete CPU-1450 assembly is only APM-based legacy power management compliant.

The core of the CPU-1450 soft power management is based on the Intel 82801 ICH2 chipset.

Figure 2. CPU-1450 Block Diagram

The colours used in the previous diagram show the different power lines used to supply peripherals during different power states. The chipset can easily understand the wake-up source.

A good point of start, to better understand the Power Management capabilities, is to refer directly to the chipset datasheet; consider that the CPU-1450 architecture is developed with the support for APM-based legacy power management for non ACPI implementations, it is not possible to refer exactly to the previous chipsets data sheets without considering some restrictions based on the hardware choices made.

The following section is intended to describe some restrictions the user needs to understand regarding the CPU-1450.

#### Intel 82801 ICH2 and System Power States

Table 1 shows the power states defined for ICH2-based platforms, the state names generally match the corresponding ACPI states, the hardware implementation of the CPU-1450 assembly does not support the greyed areas listed in the following table:

| State/Sub-states | Legacy Name / Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G0/S0/C0         | Full On: Processor operating. Individual devices may be shut down to save power. The different processor operating levels are defined by Cx states, as shown in Table 4: Transitions Rules for ICH2 Within the C0 state, the ICH2 can throttle the STPCLK# signal to reduce power consumption.                                                                                                                                                                                                                            |

| G0/S0/C1         | Auto-Halt: The processor has executed an Auto-Halt instruction and is not executing code. The processor snoops the bus and maintains cache coherency.                                                                                                                                                                                                                                                                                                                                                                     |

| G0/S0/C2         | Stop-Grant: The STPCLK# signal goes active to the processor. The processor performs a Stop-Grant cycle, halts its instruction stream, and remains in that state until the STPCLK# signal goes inactive. In the Stop-Grant state, the processor snoops the bus and maintains cache coherency.                                                                                                                                                                                                                              |

| G1/S1            | Stop-Grant: Similar to G0/S0/C2 state. The ICH2 also has the option to assert the CPUSLP# signal to further reduce processor power consumption.                                                                                                                                                                                                                                                                                                                                                                           |

| G1/S3            | Suspend-To-RAM (STR): The system context is maintained in system DRAM, but power is shut off to non-critical circuits. Memory is retained and refreshes continue. All clocks stop except RTC clock.                                                                                                                                                                                                                                                                                                                       |

| G1/S4            | Suspend-To-Disk (STD)1: The context of the system is maintained on the disk. All power is then shut off to the system except for the logic required to resume. Externally appears same as S5, but may have different wake events.                                                                                                                                                                                                                                                                                         |

| G2/S5            | Soft Off (SOFF): System context is not maintained. All power is shut off except for the logic required to restart. A full boot is required when waking.                                                                                                                                                                                                                                                                                                                                                                   |

| G3               | Mechanical OFF (MOFF): System context not maintained. All power is shut off except for the RTC. No "Wake" events are possible, because the system does not have any power. This state occurs if the user removes the batteries, turns off a mechanical switch, or if the system power supply is at a level that is insufficient to power the "waking" logic. When system power returns, transition depends on the state just prior to the entry to G3 and the AFTERG3 bit in the GEN_PMCON3 register (D31:F0, offset A4). |

Table 1. General Power States for Systems using ICH2

This table gives useful information, limited to the scope of this application note. For a more detailed description refer to 82801 ICH2 Datasheet from Intel.

<sup>&</sup>lt;sup>1</sup> Considering that the standard O.S. management usually needs an ACPI hardware platform to manage the Suspend to Disk functionality, also if the hardware allows the user to enter this mode, specific SW management, not provided by Eurotech S.p.A., needs to be developed to fulfil this mode.

#### System Power Planes

The system has several independent power planes, as described in the following table. Note that when a particular power plane is shut off, it should go to a 0V level.

| Plane  | Controlled by  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAIN   | SLP_S3# signal | When SLP_S3# goes active (low), power is shut off to any circuit not required to wake the system. Since the ACPI standard S3 state requires that the memory context be preserved, power should be retained to the main memory. However the CPU-1450 does not support the Suspend-to-Ram, so the main memory is shutdown together with the main plane. The processor, main memory, devices on the PCI bus, LPC interface, downstream hub interface and AGP will typically be shut off when the Main power plane is shut, although there may be small subsections powered. |  |

| RESUME | Always present | In this plane there are the ICH2 resume logic, Ethernet controller and others individual subsystems used for power management. This plane is powered from +5VSB OR +3V3SB. Please refer <b>Error! Reference source not found.</b> for more information.                                                                                                                                                                                                                                                                                                                  |  |

|        |                | Table 2. System power planes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

Power Management interface signals

The power management may be entered or exited depending on some specific signals listed in Table 3:

| Name            | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SLP_S3#         | Internal | Power plane control. This signal is used to shut off power to all non-critical systems when in S3 (Suspend To RAM), S4 (Suspend to Disk) or S5 (Soft Off) states                                                                                                                                                                                                                                                                                                                 |  |  |

| PWRBTN#         | Input    | The Power Button will cause SMI# or SCI to indicate a system request to go to a sleep state. If the system is already in a sleep state, this signal will cause a wake event.<br>If PWRBTN# is pressed for more than 4 seconds, this will cause an unconditional transition (power button override) to the S5 state with only the PWRBTN# available as a wake event. Override will occur even if the system is in the S1-S4 states. This signal has an internal pull-up resistor. |  |  |

| RI#             | Input    | From the modem interface. This signal can be enabled as a wake event; this is preserved across power failures.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PSON# or ATX_ON | Output   | Power-On command to ATX Power supply. When PSON# is low the ATX power supply is turned on.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| VDD             | Input    | Main power from the ATX Power supply. It can be shut off from power management controller.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| +5VSB           | Input    | +5 Volts-Always from the ATX Power supply. It is never shut off unless the user turns off a mechanical switch.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                 |          | Table 3 Dower management for interface signals                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

Table 3.Power management for interface signals

In the rest of this document we will analyse the signals considering the related programming activities.

## Event Input Signals and Their Usage

| Transitions rules for ICH2:  |                                                                                                                                         |                                                                                                                                                                       |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Present State                | Transition Trigger                                                                                                                      | Next State                                                                                                                                                            |  |  |

| G0/S0/C0                     | Processor halt instruction<br>Level 2 Read<br>Level 3 Read<br>SLP_EN bit set<br>Power Button Override<br>Mechanical Off / Power Failure | G0/S0/C1<br>G0/S0/C2<br>G0/S0/C3<br>G1/Sx or G2/S5state<br>G2/S5<br>G3                                                                                                |  |  |

| G0/S0/C1                     | Any Enabled Break Event<br>STPCLK# goes active<br>Power Button Override<br>Power Failure                                                | G0/S0/C0<br>G0/S0/C2<br>G2/S5<br>G3                                                                                                                                   |  |  |

| G0/S0/C2                     | Any Enabled Break Event<br>STPCLK# goes inactive and previously in C1<br>Power Button Override<br>Power Failure                         | G0/S0/C0<br>G0/S0/C1<br>G2/S5<br>G3                                                                                                                                   |  |  |

| G0/S0/C3<br>(ICH2-M only)    | Any Enabled Break Event<br>STPCLK# goes inactive and previously in C1<br>Power Button Override<br>Power Failure                         | G0/S0/C0<br>G0/S0/C1<br>G2/S5<br>G3                                                                                                                                   |  |  |

| G1/S1,<br>G1/S3, or<br>G1/S4 | Any Enabled Wake Event<br>Power Button Override<br>Power Failure                                                                        | G0/S0/C0 (For ICH2-M, see note 2)<br>G2/S5<br>G3                                                                                                                      |  |  |

| G2/S5                        | Any Enabled Wake Event<br>Power Failure                                                                                                 | G0/S0/C0 (For ICH2-M, see note 2)<br>G3                                                                                                                               |  |  |

| G3                           | Power Returns                                                                                                                           | Optional to go to S0/C0 (reboot) or G2/S5 (stay off until power<br>button pressed or other wake event). (For ICH2 and ICH2-M,<br>see Note 1) (For ICH2-M, see note 2) |  |  |

|                              | Table 4. Transition                                                                                                                     | ons Rules for ICH2                                                                                                                                                    |  |  |

(This page is intentionally left blank.)

# Chapter 3 CPU-1450 Power management connections

To access the Soft Power Management capabilities of the CPU-1450, specific connections need to be made; this chapter is intended to document the connections versus the wake-up devices and to supply the CPU-1450 in a Power Management compliant mode.

Considering that we support the following external wake-up capabilities:

- Wake-On-LAN

- Serial Ring Indicator

- Power Button

We will document the connections related to the previous functions and the power connections to supply the CPU, we recommend following the instructions using a CPU-1450 development system to simplify the power management testing processes.

## Ethernet

The CPU-1450 J12 connector is used for the Ethernet connection during the Wake on LAN events.

|       | J12<br>Ethernet          |

|-------|--------------------------|

| Figur | e 3. J12Connector Layout |

| Table | 5. J12 Connector pin out |

| Pin # | Signal                   |

| 1     | +3.3VSB                  |

| 2     | ACTIVITY LED             |

| 3     | RX+                      |

| 4     | RX-                      |

| 5     | LINK LED                 |

| 6     | GND                      |

| 7     | TX+                      |

| 8     | TX-                      |

#### The Eurotech Ethernet Transceiver

To establish an Ethernet connection an Ethernet Transceiver must be used. Eurotech supplies a Transceiver that can be placed between the J12 of the CPU module and the RJ45 network cable.

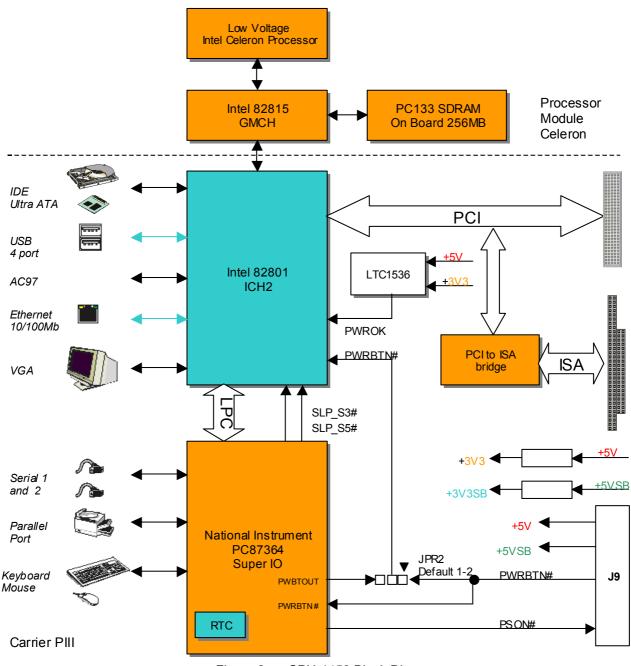

## Serial 1 & Serial 2

The CPU-1450 J8 connector is used for the Parallel, Serial 1 and Serial 2 ports. In the soft power management the *Ring Indicator* signal on the Serial sections can be used as a wake-up event. The signal level applied to the RI pins should be greater than 3V because this signal is applied to a GATE of a transistor that drives the RI pin of the ICH2. Furthermore, *the high level must be applied using a current limiting resistor*. The limiting resistor should be 1-kOhm for each volt applied, limiting the current below 1mA.

Figure 4. J8 Connector Layout

|       |             | Serial 1 |       |             |

|-------|-------------|----------|-------|-------------|

| Pin # | Description |          | Pin # | Description |

| 23    | DCD1        |          | 24    | DSR1        |

| 25    | RX1         |          | 26    | RTS1        |

| 27    | TX1         |          | 28    | CTS1        |

| 29    | DTR1        |          | 30    | RI1         |

|       |             | Serial 2 |       |             |

|-------|-------------|----------|-------|-------------|

| Pin # | Description |          | Pin # | Description |

| 31    | GND         |          | 32    | DCD2        |

| 33    | DSR2        |          | 34    | RX2         |

| 35    | RTS2        |          | 36    | TX2         |

| 37    | CTS2        |          | 38    | DTR2        |

| 39    | RI2         |          | 40    | GND         |

Table 6. J8 Connector pin out

### **Auxiliary Power Connector**

The CPU-1450 connector J9 is a 12-Pin (6x2) 2.54mm pitch connector and is used to power the module as an alternative to the PC/104-Plus bus, this connector also carries signals for power management

Auxiliary Power

Figure 5. J9 Connector layout

| Pin # | Signal    | Pin # | Signal      |

|-------|-----------|-------|-------------|

|       | GND       | 2     | VDD         |

|       | N.C.      | 4     | +12v        |

|       | -5V       | 6     | -12V        |

|       | GND       | 8     | VDD         |

|       | N.C.      | 10    | PWRBTN# (3) |

|       | +5VSB (1) | 12    | PSON# (2)   |

<sup>(1)</sup> +5VSB: +5 Volts-Always from the ATX Power supply

<sup>(2)</sup> PSON#: Power-On command to ATX Power supply

<sup>(3)</sup> *PWRBTN or Power button* : If the soft power management is enabled, a low signal in this pin turns the system on or off.

#### Notes:

The +5VSB (Volt Stand-By) voltage is useful for Power management applications only.

The +12VDC and -5VDC voltages are neither used nor generated by the CPU-1450 module: they are only conveyed on the PC/104-Plus bus (connector J1) and can be used by other devices or modules that are stacked onto the CPU module.

#### Warning:

Improper connection of the power supply will result in serious damage to the module.

## **Electrical connections**

In general if you want to supply the CPU-1450 with an ATX power supply here the connections you've to realize:

|     | J9 Aux PWR                                 |                              |     | ATX         |

|-----|--------------------------------------------|------------------------------|-----|-------------|

| Pin | Signal                                     | Description                  | Pin | Wire Colour |

| 1   | GND                                        | Ground                       | 5   | Black       |

| 2   | VDD (+5VDC)                                | +5V DC signal                | 4   | Red         |

| 3   | N.C.                                       | Not connected                |     | N.C.        |

| 4   | +12VDC                                     | +12 VDC signal               | 10  | Yellow      |

| 5   | N.C.                                       | Not connected                |     | N.C.        |

| 6   | -12VDC                                     | -12 VDC signal               | 12  | Blue        |

| 7   | GND                                        | Ground                       | 15  | Black       |

| 8   | VDD (+5VDC)                                | +5 VDC signal                | 6   | Red         |

| 9   | N.C.                                       | Not connected                |     | N.C.        |

| 10  | PWR_BTN                                    | Power Button                 |     | N.C.        |

| 11  | +5VSB                                      | Always high (ATX only)       | 9   | Purple      |

| 12  | ATX ON                                     | ATX Power on signal 14 Green |     |             |

|     | Table 7. CPU-1450 to ATX cable connections |                              |     | tions       |

#### Note:

The +12VDC and -12VDC voltages are neither used nor generated by the CPU-1450 module: they are only conveyed on the PC/104Plus bus (connector J1) and can be used by other devices or modules that are stacked onto the CPU module.

#### Warning:

Improper connection of the power supply will result in serious damage for the module.

Table 8 shows the pinout of the Standard ATX female connector with the suggested 18AWG wire colour.

| Pin | Signal           |             |     | Pin   | Signal            |

|-----|------------------|-------------|-----|-------|-------------------|

| 11  | +3.3 VDC - Oran  | ige (22AWG) |     | 1     | +3.3 VDC - Orange |

| 11  | 3.3V sense - Bro | wn (22AWG)  |     | 1     | +3.3 VDC - Orange |

| 12  | -12 VDC Blue     |             |     | 2     | +3.3 VDC - Orange |

| 13  | Black COM        |             |     | 3     | COM - Black       |

| 14  | Green PS-ON      |             |     | 4     | +5 VDC - Red      |

| 15  | Black COM        |             |     | 5     | COM - Black       |

| 16  | Black COM        |             |     | 6     | +5 VDC - Red      |

| 17  | Black COM        |             |     | 7     | COM - Black       |

| 18  | White -5 VDC     |             |     | 8     | POK - Gray        |

| 19  | Red +5 VDC       |             |     | 9     | +5VSB - Purple    |

| 20  | Red +5 VDC       |             |     | 10    | +12 VDC - Yellow  |

|     |                  | Table 8.    | ATX | Power | Connections       |

### **Development Kit connections**

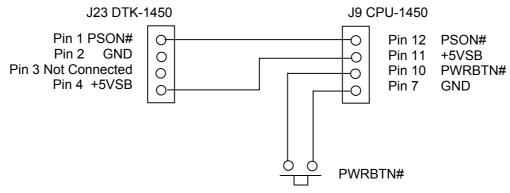

A good platform to experiment with the power saving capabilities is the Eurotech development kit; using this system you can minimize the number of power connections wired in a safe way over the motherboard. We suggest using the same reference colours listed in Table 8 with AWG18 wire. The connections you need to realize are limited and shown in the following image:

Figure 6. DTK Power Saving Connections

In this application note we assume that you are using a development system where a CPU-1450 is installed with the connections described on Figure 6.

#### Warning:

Handle the module with care, considering that the board remains supplied even when it is not operating. Remove the mains supply from the system when you need to work on the development kit.

## Chapter 4 SPM Management

The Soft Power Management capabilities of the CPU-1450 are integrated in the ICH2 82801 and the Super I/O PC87364.

The CPU has the capability to be placed in a low-power operating mode where CPU activity is stopped and power consumption reduced. Operating in this mode is possible by supplying the CPU with the power supply architecture previously described.

All wake-up event registers and related logic are battery backed-up to retain the configuration of wake-up events upon a loss of power (i.e., VDD=0V and +5VSB=0V). The battery can be connected through pin 7 (+) and pin 1 (-) of the *"Multifunction, VGA & Ethernet"* connector (J7). The Battery supply voltage must be 3.0 V (minimum 2.4 V, maximum 4.0 V).

The low power mode can be activated via software, whereas can be deactivated from either the power button or from one of a number of wake-up events.

The Soft Power Management has a few fundamental points:

- Initialise the SPM CPU peripheral to enable wake-up events

- Place the CPU in a low-power mode

- Waiting for Wake-up events

### **Entering Low Power mode**

This chapter describes how to enter the low-power mode and the events that allow the user to wake-up the CPU-1450 from the sleep state.

To minimize power consumption the CPU has to be placed into a low power consumption mode, this may be done via software.

#### ATX Power Button

If you use the ATX power-button you can shutdown the System as a standard ATX PC whenever you want, this is not a correct mode to manage the SPM mode, because, in this way your application does not have any information regarding the power on/off modes.

When you experiment with the Soft Power Management using the development kit remember to leave the ATX power button in the power off position.

#### **External Power Button**

The external Power Button (PWR\_BTN pin 10 of the J11 connector) has to be connected between pin 10 and 7 of the J11 connector to allow the user to power-down or power-up the CPU. This feature may be enabled or disabled by writing the appropriate values on the ICH2 registers.

Looking at the **Error! Reference source not found.** users can analyse the PWR\_BTN signal path that can be routed via the JPR2 to the ICH2 82801 or the Super I/O PC87364. By default the PWR\_BTN signal is routed to the ICH2 chipset.

Currently this functionality is not implemented.

#### Software

You can enter Low Power Mode by writing to the appropriate register using software; this allows you to shutdown the CPU remotely. The SPM may be managed by software by programming the Software Power Down Registers as described later in this document.

### Wake-up events

The hardware of the CPU-1450 has been developed to allow the user to manage the Soft Power Management modes with the following wake-up event sources:

- Serial Port Ring Indicator pin

- Ethernet

- External Power Button

- Wake on RTC

All the possible wake-up events can be enabled or disabled by setting the Soft Power Enable Registers. The user can also know what event has occurred to turn-on the power by reading the Soft Power Status Registers. Note that the status bit gets set if the wake-up event occurs, whether or not it is enable as a wake-up function by setting the corresponding bit in Soft Power Enable Register. However only the enabled wake-up functions will turn the system power on.

#### Serial port Ring Indicator

The hardware wake-up event from the sleeping state is activated with a high signal at this pin. Levels should be greater than 3V because this signal is applied to a GATE of a transistor that drives the RI pin of the ICH2. Furthermore *the high level must be applied using a current limiting resistor*, the limiting resistor has to be 1kOhm for each volt applied, limiting the current below 1mA.

Note that Filtering / De-bounce on RI# will not be done in ICH2 or in CPU-1450.

Please refer to Chapter 6 for a practical example using the wake on nRINGING functionality.

#### Ethernet

The CPU-1450 module uses the Ethernet controller integrated into ICH2. This controller is compliant to ACPI (Rev. 1.0), PCI Power management (Rev 1.0) and monitors the network looking for a Wake-up Frame, a Magic Packet or a Link change and notifies the event via the internal PME# signal.

#### Magic Packet from the network

A remote Computer can utilize the Magic packet\* to wake-up the module. Once the Module has been enabled for Magic Packet\* wake-up and has been put into appropriate state, it scans all incoming packets addressed to the node for a specific data sequence, which indicates to the controller that this is a Magic Packet\* frame must also meet the basic requirements: Destination address + Source address + data + CRC. The destination address may be the node ID of the receiving station or a multicast address, which includes the broadcast address. The specific sequence consists of 16 duplications of the 6-byte ID registers, with no breaks or interrupts. This sequence can be located anywhere within the packet, but must be preceded by a synchronization stream, 6 bytes of FFh. The device will also accept a multicast address, as long as the 16 duplications of the IEEE address match the address of the ID registers. If the Node ID is 11h 22h 33h 44h 55h 66h, then the magic frame's format is like the following:

Destination address + source address + MISC + FF FF FF FF FF FF FF FF + MISC + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 33 44 55 66 + 11 22 3

Please refer to Chapter 6 for a practical example using the Magic Packet functionality.

#### External Power Button PWRBTN#

A low signal in the Power Button pin (if enabled) can be used to turn-on or turn-off the system from the low power mode. A low level at this pin activates the wake-up functionality.

#### Wake on RTC

A hardware wake-up event from the sleeping state can be made at a predetermined time with an RTC alarm. In this case please be careful that the RTC is upgraded (Eurotech BIOS provides a user friendly interface to update the time and date), users have to initialise the RTC alarm registers and place the CPU into Low power consumption mode, when RTC reach RTC alarm count the CPU is waked up.

Please refer to Chapter 6 for a practical example using the Wake on RTC functionality.

# Chapter 5 Soft Power Management Registers

The SPM register model consists of a number of fixed register blocks that perform designated functions. A register block consists of a number of registers that perform Status, Enable and Control Functions.

- Status bits are only set through some defined hardware events.

- Unless otherwise noted, Status bits are cleared by writing a HIGH to that bit position, and upon VTR POR. Writing 0 has no effect.

- Status bits only generate interrupts while their associated bit in the enable register is set.

- Function bit positions in the status register have the same bit position in the enable register.

Wake-up event configuration is retained by the battery backup power.

For a first approach to power management it is not required to know all the registers involved.

The program examples in the next chapter set the power mode as required for a quick test of power management.

As a reference, for a more detailed approach, the following pages show a list of interesting registers used in the code examples.

## Intel® 82801BA I/O Controller Hub 2 (ICH2)

The following tables report the ICH2 registers useful for the power management.

| Name    | Address                                                               | Function                                                                                            |

|---------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| PMCSR   | PCI Configuration Register<br>Bus 1, Device 8, Function 0, offset E0h | Power Management Control/Status Register of LAN Controller. Used to enable PME and set Power State. |

| PM1_STS | I/O address 6000h                                                     | Power Management 1 Status Register. Used to read and clear wake status.                             |

| PM1_EN  | I/O address 6002h                                                     | Power Management 1 Enable Register. Used to enable wake events as RTC.                              |

| PM1_CNT | I/O address 6004h                                                     | Power Management 1 Control Register. Used to set sleep modes.                                       |

| GPE0_EN | I/O address 602Ah                                                     | General Purpose Event 0 Enables Register. Used to enable wake events as Ring Indicator and PME.     |

|         | Table 9. Inter                                                        | esting ICH2 registers                                                                               |

For a more detailed description please refer to Intel® 82801BA I/O Controller Hub 2 (ICH2) datasheet.

#### PM1\_STS Power Management 1 Status Register

| I/O Address                   | 6000h                                                        |  |

|-------------------------------|--------------------------------------------------------------|--|

| (ACPI PM1a_EVT_BLK) Attribute | R/WC                                                         |  |

| Default Value                 | 0000h                                                        |  |

| Size                          | 16-bit                                                       |  |

| Lockable                      | No                                                           |  |

| Usage                         | ACPI or Legacy                                               |  |

| Power Well                    | Bits 0–7: Core,<br>Bits 8–15: Resume<br>Except Bit 11 in RTC |  |

If bit 10 or 8 in this register is 1 and the corresponding \_EN bit is set in the PM1\_EN register, ICH2 generates a Wake Event. Once back in an S0 state (or if already in S0 state when the event occurs), ICH2 also generates an SCI if the SCI\_EN bit is set or an SMI# if the SCI\_EN bit is not set.

*Note:* Bit 5 does not cause an SMI# or a wake event. Bit 0 does not cause a wake event but can cause an SMI# or SCI.

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | <ul> <li>Wake Status (WAK_STS)—R/WC. This bit is not affected by hard resets caused by a CF9 write but is reset by RSMRST#.</li> <li>0 = Software clears this bit by writing a 1 to the bit position.</li> <li>1 = Set by hardware when the system is in one of the sleep states (via the SLP_EN bit) and an enabled wake event occurs.</li> <li>Upon setting this bit, the ICH2 will transition the system to the ON state.</li> <li>If the AFTERG3_EN bit is not set and a power failure occurs without the SLP_EN bit set, the system will return to an S0 state when power returns, and the WAK_STS bit will not be set. For the 82801BAM ICH2-M, power failure could result from removing the batteries.</li> <li>If the AFTERG3_EN bit is set and a power failure occurs without the SLP_EN bit having been set, the system will go into an S5 state when power returns and a subsequent wake event will cause the WAK_STS bit to be set. Note that any subsequent wake event would have to be caused by either a Power Button press or an enabled wake event that was preserved through the power failure (enable bit in the RTC well).</li> </ul> |

| 14:12 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11    | Power Button Override Status (PRBTNOR_STS)—R/WC. This bit is not affected by hard resets caused by a CF9 write and is<br>not reset by RSMRST#. Thus, this bit will be preserved through a power failure.<br>0 = The BIOS or SCI handler can clear this bit by writing a 1 to it.<br>1 = Set by hardware anytime a Power Button Override Event occurs which occurs when the power button is pressed for at least<br>4 consecutive seconds. The power button override causes an unconditional transition to the S5 state and sets the AFTERG3 bit.<br>This bit can also be set by the SMBus Slave logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10    | RTC Status (RTC_STS)—R/WC. This bit is not affected by hard resets caused by a CF9 write but is reset by RSMRST#.<br>0 = Software clears this bit by writing a 1 to the bit position.<br>1 = Set by hardware when the RTC generates an alarm (assertion of the IRQ8# signal). Additionally if the RTC_EN bit is set, the setting of the RTC_STS bit will generate a wake event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8     | Power Button Status (PWRBTN_STS)—R/WC. This bit is not affected by hard resets caused by a CF9 write.<br>1 = This bit is set by hardware when the PWRBTN# signal is asserted Low, independent of any other enable bit.<br>In the S0 state, while PWRBTN_EN and PWRBTN_STS are both set, an SCI (or SMI# if SCI_EN is not set) will be generated. In<br>any sleeping state S1–S5, while PWRBTN_EN and PWRBTN_STS are both set, a wake event is generated.<br>0 = If the PWRBTN# signal is held low for more than 4 seconds, the hardware clears the PWRBTN_STS bit, sets the<br>PWRBTNOR_STS bit, and the system transitions to the S5 state with only PWRBTN# enabled as a wake event. This bit can be<br>cleared by software by writing a one to the bit position.                                                                                                                                                                                                                                                                                                                                                                                       |

| 7:6   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5     | Global Status (GBL_STS)—R/WC.<br>1 = Set when an SCI is generated due to BIOS wanting the attention of the SCI handler. BIOS has a corresponding bit,<br>BIOS_RLS, which will cause an SCI and set this bit.<br>0 = The SCI handler should then clear this bit by writing a 1 to the bit location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4     | ICH2 (82801BA):<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3:1   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0     | Timer Overflow Status (TMROF_STS)—R/WC.<br>1 = This bit gets set any time bit 22 of the 24-bit timer goes high (bits are numbered from 0 to 23).<br>This will occur every 2.3435 seconds. When the TMROF_EN bit is set, then the setting of the TMROF_STS bit will additionally<br>generate an SCI or SMI# (depending on the SCI_EN).<br>0 = The SCI or SMI# handler clears this bit by writing a 1 to the bit location.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Table 10.         PM1_STS Power Management 1 Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## PM1\_EN—Power Management 1 Enable Register

| I/O Address                   | 6002h                   |                 |

|-------------------------------|-------------------------|-----------------|

| (ACPI PM1a_EVT_BLK) Attribute | R/W                     |                 |

| Default Value                 | 0000h                   |                 |

| Size                          | 16-bit                  |                 |

| Lockable                      | No                      |                 |

| Usage                         | ACPI or Legacy          |                 |

| Power Well                    | Bits 0–7:<br>Bits 8–15: | Core,<br>Resume |

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                           |

| 10    | RTC Event Enable (RTC_EN)—R/W. This bit is in the RTC well to allow an RTC event to wake after<br>a power failure. This bit is not cleared by any reset other than RTCRST# or a Power Button Override<br>event.<br>1 = An SCI (or SMI#) or wake event will occur when this bit is set and the RTC_STS bit goes active.<br>0 = No SCI (or SMI#) or wake event is generated then RTC_STS goes active. |

| 8     | Power Button Enable (PWRBTN_EN)—R/W. This bit is used to enable the setting of the PWRBTN_STS bit to generate a power management event (SMI#, SCI). PWRBTN_EN has no effect on the PWRBTN_STS bit being set by the assertion of the power button. The Power Button is always enabled as a Wake event.<br>0 = Disable.<br>1 = Enable.                                                                |

| 5     | Global Enable (GBL_EN)—R/W. When both the GBL_EN and the GBL_STS are set, an SCI is raised.<br>0 = Disable.<br>1 = Enable SCI on GBL_STS going active.                                                                                                                                                                                                                                              |

| 0     | Timer Overflow Interrupt Enable (TMROF_EN)—R/W. Works in conjunction with the SCI_EN bit as described below:<br>TMROF_EN SCI_EN Effect when TMROF_STS is set<br>0 x No SMI# or SCI<br>1 0 SMI#<br>1 1 SCI                                                                                                                                                                                           |

|       | Table 11. PM1_EN—Power Management 1 Enable Register                                                                                                                                                                                                                                                                                                                                                 |

## PM1\_CNT—Power Management 1 Control Register

| I/O Address                   | 6004h                   |                 |

|-------------------------------|-------------------------|-----------------|

| (ACPI PM1a_EVT_BLK) Attribute | R/W                     |                 |

| Default Value                 | 0000h                   |                 |

| Size                          | 32-bit                  |                 |

| Lockable                      | No                      |                 |

| Usage                         | ACPI or Legacy          |                 |

| Power Well                    | Bits 0–7:<br>Bits 8–15: | Core,<br>Resume |

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13    | Sleep Enable (SLP_EN)—WO. Setting this bit causes the system to sequence into the Sleep state defined by the SLP_TYP field.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12:10 | Sleep Type (SLP_TYP)—R/W. This 3-bit field defines the type of Sleep the system should enter when the SLP_EN bit is set to<br>1.<br>000 = ON: Typically maps to S0 state.<br>011 = Reserved<br>100 = Reserved<br>101 = Suspend-To-RAM. Assert SLP_S1# and SLP_S3#; typically, maps to S3 state.<br>110 = Suspend-To-Disk. Assert SLP_S1#, SLP_S3#, and SLP_S5# SLP_S3# and, SLP_S5#; typically, maps to S4 state.<br>111 = Soft Off. Assert SLP_S1#, SLP_S3#, and SLP_S5# SLP_S3#, and SLP_S5#; typically, maps to S5 state.                     |

| 2     | Global Release (GBL_RLS)—WO.<br>1 = ACPI software writes a 1 to this bit to raise an event to the BIOS. BIOS software has corresponding enable and status bits<br>to control its ability to receive ACPI events.<br>0 = This bit always reads as 0.                                                                                                                                                                                                                                                                                              |

| 1     | ICH2 (82801BA):<br>Reserved<br>ICH2-M (82801BAM):<br>Bus Master Reload (BM_RLD)— R/W. This bit is reset to 0 by PCIRST#<br>0 = Bus master requests do not cause a break from the C3 state.<br>1 = Enable Bus Master requests (internal, external or AGPBUSY#) to cause a break from the C3 state.                                                                                                                                                                                                                                                |

| 0     | SCI Enable (SCI_EN)—R/W. Selects the SCI interrupt or the SMI# interrupt for various events including the bits in the PM1_STS register (bit 10, 8, 0), and bits in GPE0_STS.<br>0 = These events will generate an SMI#.<br>1 = These events will generate an SCI.<br>001 = ICH2 (82801BA): Assert STPCLK#. Puts processor in Stop-Grant state. Optional to assert<br>CPUSLP# to put processor in sleep state: Typically, maps to S1 state.<br>ICH2-M (82801BAM): Reserved.<br>010 = ICH2 (82801BA): Assert SLP_S1#: Typically, maps to S1 state. |

|       | Table 12. PM1_CNT—Power Management 1 Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### GPE0\_EN—General Purpose Event 0 Enables Register

| I/O Address                   | 602h                    |              |

|-------------------------------|-------------------------|--------------|

| (ACPI PM1a_EVT_BLK) Attribute | R/W                     |              |

| Default Value                 | 0000h                   |              |

| Size                          | 16-bit                  |              |

| Lockable                      | No                      |              |

| Usage                         | ACPI                    |              |

| Power Well                    | Bits 0–7:<br>Bits 8–15: | Core,<br>RTC |

*Note:* This register is symmetrical to the General Purpose Event 0 Status Register. All the bits in this register should be cleared to 0 based on a Power Button Override. The resume well bits are all cleared by RSMRST#. The RTC sell bits are cleared by RTCRST#.

| Bit   | Description                                                                                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved.                                                                                                                                                                                                                                                                 |

| 11    | PME# Enable (PME_EN)—R/W.<br>0 = Disable.<br>1 = Enables the setting of the PME_STS to generate a wake event and/or an SCI. PME# can be a wake event from the S1–S4<br>state or from S5 (if entered via SLP_EN, but not power button override).                           |

| 10    | ICH2 (82801BA):<br>Reserved                                                                                                                                                                                                                                               |

| 9     | Reserved                                                                                                                                                                                                                                                                  |

| 8     | RI_EN—R/W. The value of this bit will be maintained through a G3 state and is not affected by a hard reset caused by<br>RSMRST# or a CF9h write. Assertion of RTCRST# resets this bit.<br>0 = Disable.<br>1 = Enables the setting of the RI_STS to generate a wake event. |

| 7     | Reserved                                                                                                                                                                                                                                                                  |

| 6     | TCO SCI Enable (TCOSCI EN)—R/W.                                                                                                                                                                                                                                           |

|       | 0 = Disable.<br>1 = Enables the setting of the TCOSCI_STS to generate an SCI.                                                                                                                                                                                             |

| 5     | AC97 Enable (AC97_EN)—R/W.<br>0 = Disable.<br>1 = Enables the setting of the AC97_STS to generate a wake event.                                                                                                                                                           |

| 4     | USB Controller 2 Enable (USB2_EN)—R/W.<br>0 = Disable.<br>1 = Enables the setting of the USB2_STS to generate a wake event.                                                                                                                                               |

| 3     | USB Controller 1 Enable (USB1_EN)—R/W.<br>0 = Disable.<br>1 = Enables the setting of the USB1_STS to generate a wake event.                                                                                                                                               |

| 2     | Thermal Pin Polarity (THRM#_POL)—R/W. This bit controls the polarity of the THRM# pin needed to set the THRM_STS bit.<br>0 = Low value on the THRM# signal will set the THRM_STS bit.<br>1 = HIGH value on the THRM# signal will set the THRM_STS bit.                    |

| 1     | Reserved                                                                                                                                                                                                                                                                  |

| 0     | Thermal Signal Reporting Enable (THRM_EN)—R/W.<br>0 = Disable.<br>1 = Active assertion of the THRM# signal (as defined by the THRM_POL bit) will set the<br>THRM_STS bit and generate a power management event (SCI or SMI).                                              |

|       | Table 13.       GPE0_EN—General Purpose Event 0 Enables Register                                                                                                                                                                                                          |

### **SuperIO National PC87364**

The following tables show the National Super I/O PC87364 registers useful for the power management: